## Written exam with solutions IE1204/5 Digital Design Friday 13/1 2017 08.00-12.00

### **General Information**

Examiner: Ingo Sander.

*Teacher*: Kista, William Sandqvist tel 08-7904487 *Teacher*: Valhallavägen, Ahmed Hemani 08-7904469

Exam text does not have to be returned when you hand in your writing.

*Aids:* No aids are allowed! The exam consists of three parts with a total of 14 tasks, and a total of 30 points:

**Part A1 (Analysis)** containes ten short questions. Right answer will give you one point. Incorrect answer will give you zero points. The total number of points in Part A1 is 10 points. To pass the **Part A1 requires at least 6p**, *if fewer points we will not look at the rest of your exam*.

Part A2 (Methods) contains two method problems on a total of 10 points.

To **pass the exam** requires at least **11 points** from A1 + A2, *if fewer points we will not look at the rest of your exam*.

Part B (Design problems) contains two design problems of a total of 10 points. Part B is

corrected only if there are at least 11p from the exam A- Part.

**NOTE !** At the end of the exam text there is a submission sheet for Part A1, which shall be

separated and be submitted together with the solutions for A2 and B.

For a passing grade (E) requires at **least 11 points on the exam**. If exactly 10p from A1(6p)+A2(4p), (FX), completion to (E) will be offered.

Grades are given as follows:

| 0 – | 11 – | 16 – | 19 – | 22 – | 25 |

|-----|------|------|------|------|----|

| F   | Е    | D    | С    | В    | А  |

The result is expected to be announced before Friday 3/2 2017.

### Part A1: Analysis

Only answers are needed in Part A1. Write the answers on the submission sheet for Part A1, which can be found at the end of the exam text.

**1.** 1p/0p

A function f(x, y, z) is described om minimized SoP form (Sum of products):

$f(x, y, z) = \{SoP\}_{\min} = y + x \cdot \overline{z}$

Write down the function as a minimized product of sums.

$$f(x, y, z) = \{PoS\}_{\min} = ?$$

1. Proposed solution.

$$f(x, y, z) = \{SoP\}_{\min} = y + x \cdot \overline{z}$$

$$yz \quad f$$

$$yz \quad f$$

$$yz \quad 00 \quad 01 \quad 11 \quad 10$$

$$yz \quad 00 \quad 01 \quad 11 \quad 10$$

$$f(x, y, z) = \{PoS\}_{\min} = (x + y) \cdot (y + \overline{z})$$

$$f(x, y, z) = \{PoS\}_{\min} = (x + y) \cdot (y + \overline{z})$$

#### **2.** 1p/0p

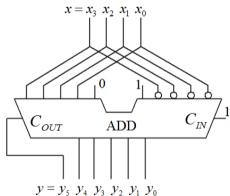

Useless circuit (!). A 5-bit adder is connected to multiply a binary unsigned 4-bit number  $x = x_3x_2x_1x_0$  with a constant k,  $y = k \cdot x$ . Let the number x be  $x = 1010_2$  what will the (6 bit) sum  $y = y_5y_4y_3y_2y_1y_0$  be?

2. Proposed solution.

If ignoring Carry out (5 bit sum) the circuit performs the operation  $y = (2 \cdot x - 1 \cdot x) = 1 \cdot x$  the number x remains unaffected by adder (k = 1). 1010  $\rightarrow$  01010. With Carry out (the 6 bit sum) 1010  $\rightarrow$  101010.

Yes this circuit is realy useless outside the exam (where it is worth 1p).

#### **3.** 1p/0p

A two's complement 16-bit number is  $x_{16}$  = FFFB (hexadecimal). This number will be transferred to a 4-bit register (the number of bits will be reduced and the sign kept). Express this 4-bit number as a decimal number with sign  $\pm x_{10}$  = ?

3. Proposed solution.

The twelve excess sign bits are ignored  $x = B = 1011 = -(0100+1) = -0101_2 = -5_{10}$

#### **4**. 1p/0p

Given is a Karnaugh map for a function of four variables  $Y = f(x_3, x_2, x_1, x_0)$ . Write the function  $Y_{min}$ , as a minimized sum of products, on **SoP** form. "-" in the map means "don't care".

| x <sub>3</sub> x <sub>2</sub> x <sub>1</sub> | ×0<br>00       | 01         | 11              | 10             |

|----------------------------------------------|----------------|------------|-----------------|----------------|

| 00                                           | <sup>0</sup> 1 | T <b>-</b> | ° <b>1</b>      | <sup>2</sup> 0 |

| 01                                           | 4 -            | 5          | <sup>7</sup> 1  | <sup>6</sup> 0 |

| 11                                           | 1 <b>0</b>     | 13         | 15              | <sup>14</sup>  |

| 10                                           | 8 <b>0</b>     | 9          | <sup>11</sup> 1 | 10             |

#### 4. Proposed solution.

| x <sub>3</sub> x <sub>2</sub> x <sub>1</sub> | ×0<br>00   | 01             | 11             | 10                        |

|----------------------------------------------|------------|----------------|----------------|---------------------------|

| 00                                           | 01         | 1-             | <sup>3</sup> 1 | <sup>2</sup> 0            |

| 01                                           | 4          | <sup>5</sup> 1 | <sup>7</sup> 1 | <sup>6</sup> 0            |

| 11                                           | 1 <b>0</b> | í <b>1</b>     | 11             | <sup>1</sup> <sup>4</sup> |

| 10                                           | 80         | 9-             | 14             | 10<br>_                   |

$$Y_{\min} = f(x_3, x_2, x_1, x_0) = f(x_3, x_1, x_0) =$$

=  $x_0 + \overline{x_3 x_1} + x_3 x_1 = x_0 + \overline{x_3 \oplus x_1}$

#### 5. 1p/0p

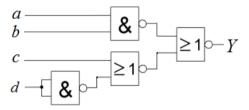

The figure below shows a circuit with two NOR gates and two NAND gates. Simplify the function Y = f(a, b, c, d) as much as possible and write the function on SoP-form.

**5.** Proposed solution.

$$Y = \overline{a \cdot b} + (c + \overline{d}) = \left\{ dM \right\} = a \cdot b \cdot (c + \overline{d}) = abc + ab\overline{d}$$

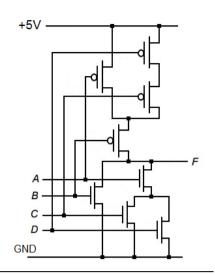

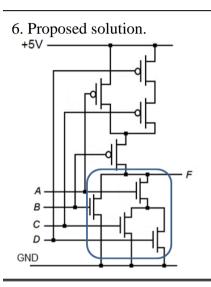

**6.** 1p/0p Give an expression for the logical function realized by the CMOS circuit in the figure. Write the function on SoP-form. F = f(A, B, C, D) = ?

Pulldown net  $\overline{F} = B + A \cdot (C + D)$   $\Rightarrow F = \overline{B + A \cdot (C + D)} = \overline{B} \cdot \overline{A \cdot (C + D)} =$   $= \overline{B} \cdot (\overline{A} + (\overline{C + D})) = \overline{B} \cdot (\overline{A} + \overline{C} \cdot \overline{D}) = \overline{B} \cdot \overline{A} + \overline{B} \cdot \overline{C} \cdot \overline{D}$

#### **7**. 1p/0p

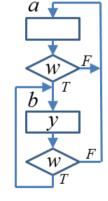

A State Machine can be drawn either as **state diagram** or as **ASM chart** (Algorithmic State Machine chart).

This figure shows an ASM-chart. Draw the equivalent **Moore state diagram** using the circles in the right figure.

The same figure is also on the submission sheet.

7. Proposed solution.

**8**. 1p/0p

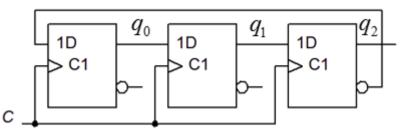

A synchronous counter starts in the state  $q_2q_1q_0 = 000$ . What will the state be after **four** clock pulses?  $q_2q_1q_0 = ?$

#### 8. Proposed solution.

The counter is a Moebius counter that counts the "Creeping Code".

$$q_2 q_1 q_0: 000 \rightarrow 001 \rightarrow 011 \rightarrow 111 \rightarrow 110 \qquad q_2 q_1 q_0 = 110$$

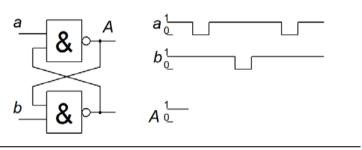

#### **9.** 1p/0p

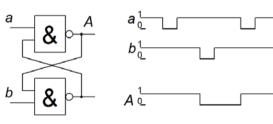

The figure shows a latch circuit. Complete the timing diagram. The same timing diagram is also on the submission sheet.

#### 9. Proposed solution.

**10.** 1p/0p

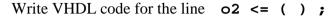

At the labs, we use chips from the 74-series. They are nowadays used as spares. These functions can instead be described using VHDL code and downloaded to programmable logic.

The circuit 7421 is shown to the right. Below are the VHDL code for the circuit. In the code, we have hidden the line **o1** from you (with characters  $\bullet$ ).

```

library ieee;

use ieee.std_logic_1164.all;

entity A74XX21 is

port (

al : in std_logic;

b1 : in std_logic;

c1 : in std_logic;

d1 : in std_logic;

a2 : in std_logic;

b2 : in std_logic;

c2 : in std_logic;

d2 : in std_logic;

o1 : out std_logic;

o2 : out std_logic );

end entity;

architecture dataflow of A74XX21 is

begin

01 <= (

);

02 <= (

);

```

end architecture;

**10.** Proposed solution.

o2 <= ( a2 and b2 and c2 and d2 ) ;

## Part A2: Methods

*Note! Part A2 will only be corrected if you have passed part A1* ( $\geq 6p$ )

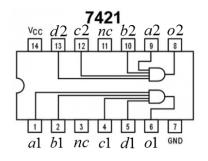

#### **11.** 4p **ANDON** signal lights.

In production factories with assembly line a system of warning lights green (G), yellow (Y) and Red (R) are used at the assembly stations. Operators have a stop button (with a cord) that stops the assembly line and all stations then signals **red**. The operator also has an alert button to summon help. It will signal **yellow** light at the own station and for all previous stations along the assembly line, but without stopping it.

When all problems are removed, the assembly line may be started again with a short start pulse (Start). All stations then signals the green light. See the figure that shows three stations with the operator buttons and lights. The arrow indicates the transport direction of the assembly line.

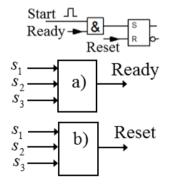

**a**) (a+b=1p) (**Green**) A short pulse Start = 1 can start the assembly line *if* Ready = 1. Design a circuit that provides signal Ready = 1 if *none* of the stop signals  $s_1 s_2 s_3$  are 1.

**b**) (**Red**) The assembly line is stopped if Reset =1. Design a circuit that provides signal Reset = 1 if *any* of the signals  $s_1$   $s_2$   $s_3$  is 1.

Reset =  $f(s_1, s_2, s_3)$ .

Draw the two circuits together, use a few optional gates.

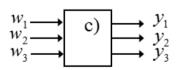

c) (2p) (Yellow) Operators can warn on problems by lighting a yellow lamp. The signals  $w_1 w_2 w_3$  shall lit their own yellow light ( $y_1$  at  $w_1$  or  $y_2$  at  $w_2$  or  $y_3$  at  $w_3$ ), but also lit the yellow lights belonging to the stations that are earlier in the direction of assembly line (stations after shall not be warned).

Set up the truth table for  $y_1y_2y_3 = f(w_1, w_2, w_3)$ .

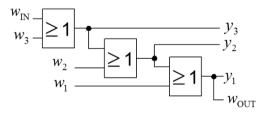

Derive the functions  $y_1 = f(w_1, w_2, w_3)$   $y_2 = f(w_1, w_2, w_3)$   $y_3 = f(w_1, w_2, w_3)$  by inspecting the truth table or by using Karnaugh map. Design the circuit with a few optional gates.

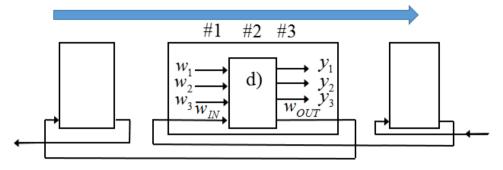

**d**) (1p) It is common with more than three workstations along a conveyor belt. In the figure, a warning signal  $w_{\text{IN}}$  from an subsequent group of stations, and a warning signal  $w_{\text{OUT}}$  to a previous group of stations, has been added.

Completed the circuit from c) with the signals signal  $w_{OUT}$  and  $w_{IN}$  in such a way that it works together with the other stations. (Rule: all previous stations must also warn with yellow light).

11. Proposed solution.

**a**) Ready =

$$\bar{s}_1 \cdot \bar{s}_2 \cdot \bar{s}_3 = \bar{s}_1 \cdot \bar{s}_2 \cdot \bar{s}_3 = \{dM\} = \bar{s}_1 + \bar{s}_2 + \bar{s}_3$$

**b**) Reset =  $s_1 + s_2 + s_3$

| <b>c</b> ) |       |       |       |                 |       |                 |  |  |

|------------|-------|-------|-------|-----------------|-------|-----------------|--|--|

|            | $w_1$ | $w_2$ | $W_3$ | $\mathcal{Y}_1$ | $y_2$ | $\mathcal{Y}_3$ |  |  |

|            | 0     | 0     | 0     | 0               | 0     | 0               |  |  |

|            | 0     | 0     | 1     | 1               | 1     | 1               |  |  |

|            | 0     | 1     | 0     | 1               | 1     | 0               |  |  |

|            | 0     | 1     | 1     | 1               | 1     | 1               |  |  |

|            | 1     | 0     | 0     | 1               | 0     | 0               |  |  |

|            | 1     | 0     | 1     | 1               | 1     | 1               |  |  |

|            | 1     | 1     | 0     | 1               | 1     | 0               |  |  |

|            | 1     | 1     | 1     | 1               | 1     | 1               |  |  |

$$w_{1} w_{2} w_{3} v_{2}$$

$$w_{1} 00 01 11 10$$

$$0 0 1 1 1 1$$

$$y_{2} = \overline{w_{2}} w_{3} = w_{2} + w_{3}$$

$$y_{3} = w_{3} \text{ (inspection of t-table)}$$

$$y_{1} = w_{1} + w_{2} + w_{3} \text{ (inspection)}$$

$$y_{2} = w_{2} + w_{3} \text{ (K-map)}$$

**d**)

$$w_{IN}$$

is or-ed together with  $w_3$ .

$y_3 = (w_3 + w_I)$

$y_2 = w_2 + (w_3 + w_I)$

$y_1 = w_1 + w_2 + (w_3 + w_{IN})$

$w_{OUT}$  will now be the same as  $y_1$ .

$w_{OUT} = y_1 = w_1 + w_2 + (w_3 + w_I)$

$\geq$  1

$S_1$

$S_2$

$W_3$

$W_2$

$W_1$

1 – Ready

Reset

$y_3$

$y_2$

$y_1$

≥1

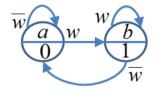

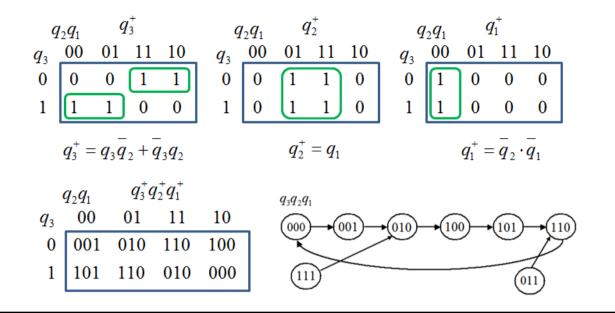

#### 12.6p Counter

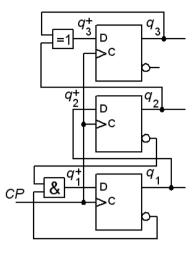

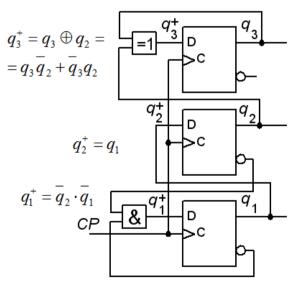

A modulo-6 synchronous counter consists of three D-flip-flops and one XOR-gate and one AND-gate, se the figure.

a) (1p) Derive the expressions for next state

$q_3^+ = ?$   $q_2^+ = ?$   $q_1^+ = ?$

**b**) (1p) Set up the complete state table  $q_3^+q_2^+q_1^+ = f(q_3q_2q_1)$

c) (1p) Draw the complete state diagram.

**d**) (1p) Which states are not part of the modulo-6 sequence? What will happen if one starts from any of these states?

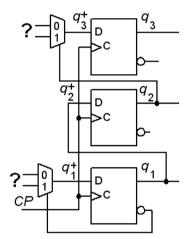

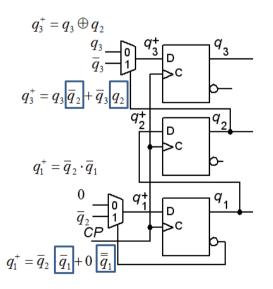

Redesign the circuit, maintaining the function so that it uses **two 2:1 multiplexers** in place of the gates. See figure to the right.

**e**) (2p) What signals should be connected to the multiplexer data inputs to replace the gates?

$$q_3^+: mux_0 = ?, \quad mux_1 = ?$$

$q_1^+: mux_0 = ?, \quad mux_1 = ?$

12. Proposed solution.

## Part B. Design Problems

*Note!* Part B will only be corrected if you have passed part  $A1+A2 (\geq 11p)$ .

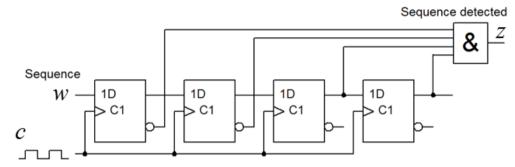

13. 5p Synchronous sequential circuit. Detector for specific event.

A shift register is used to detect when a particular sequence occurs in a sequence of bits to input w. The signal w is synchronized with the clock pulses c. Each time the correct bit sequence appears z = 1. At start is w = 0.

**a**) (1p) Which bit sequence is detected?

One can construct a Moore machine with fewer D-flip-flops that detects the same sequence.

**b**) (1p) Draw the **State Diagram** for such a sequence detector.

c) (2p) Derive the **state table** and the **coded state table**, using *binary code* as state code. Derive minimized expressions for **next state decoder** and **output decoder**. You do not need to draw any circuit diagram.

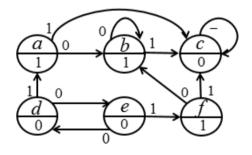

**d**) (1p) Minimize the following state diagram. Then draw the minimized **state diagram**.

Note that this is a completely independent task without any connection to the former sequence detector.

13. Proposed solution.

**a**) The input sequence will be  $1 \rightarrow 1 \rightarrow 0 \rightarrow 0$ .

b)

c)

| ,                 | _                            | $q_{1}^{+}q_{0}^{+}$ |                    | $q_1^+$ $q_1^+$ $q_0^+$                                                                                                                                  |

|-------------------|------------------------------|----------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| $q_{2}q_{1}q_{0}$ | 0                            | w<br>1               | Ζ                  | $q_0 w$ $q_0 w$ $q_0 w$                                                                                                                                  |

| 000               | 000                          | 001                  | 0                  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                     |

| 001               | 000                          | 010                  | 0                  | 01 0 0 0 1 01 1 0 0 0 01 1 0 1 0                                                                                                                         |

| 010               | 011                          | 010                  | 0                  |                                                                                                                                                          |

| 011               | 100                          | 001                  | 0                  | 10  0  0  -  -  10  0  0  -  -  10  0  1  -  -                                                                                                           |

| 100               | 000                          | 001                  |                    |                                                                                                                                                          |

| $z = q_2$         | $q_2^{\scriptscriptstyle +}$ | $= q_1 q_1$          | $q_0 \overline{w}$ | $q_1^+ = q_1 \overline{q_0} \overline{w} + \overline{q_1} q_0 w$ $q_0^+ = q_1 \overline{q_0} \overline{w} + \overline{q_1} \overline{q_0} w + q_1 q_0 w$ |

| <b>d</b> ) Ind    | epend                        | lent t               | ask.               |                                                                                                                                                          |

|                   | $0^w$                        | 1                    | $\overline{z}$     | (abf)(cde)                                                                                                                                               |

|                   |                              |                      | -                  | $a_0 \rightarrow (abf)  a_1 \rightarrow (cde) \qquad A = (abf)  B = (c)$                                                                                 |

| а                 | b                            | С                    | 1                  | $b_0 \rightarrow (abf)  b_1 \rightarrow (cde) \qquad C = (de)$                                                                                           |

| b                 | b                            | с                    | 1                  | $f_0 \rightarrow (abf)$ $f_1 \rightarrow (cde)$ $0 \qquad 0 \qquad 1 \qquad z \qquad 0 \qquad A \qquad 1 \qquad B$                                       |

| С                 | с                            | с                    | 0                  | (abf)() $A A B 1 1$                                                                                                                                      |

| d                 | е                            | а                    | 0                  | $c_0 \rightarrow (cde)  c_1 \rightarrow (cde)$<br>B  B  B  B  0  C                                                                                       |

| е                 | d                            | f                    | 0                  | $a_0 \rightarrow (cde)  a_1 \rightarrow (abf)$                                                                                                           |

| f                 | b                            | с                    | 1                  | $e_0 \rightarrow (cde)  e_1 \rightarrow (abf) \qquad C  C  A  0$<br>(abf)(c)(de)                                                                         |

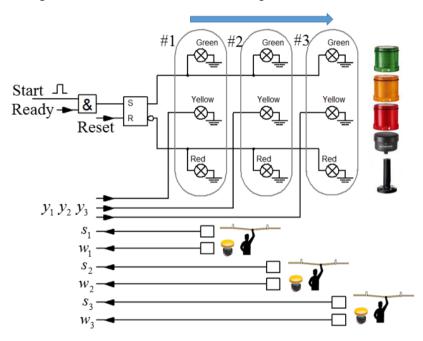

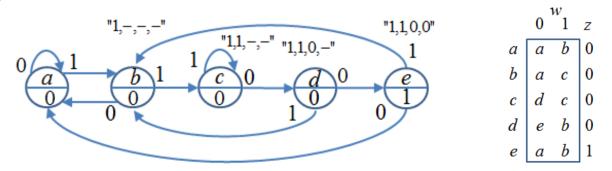

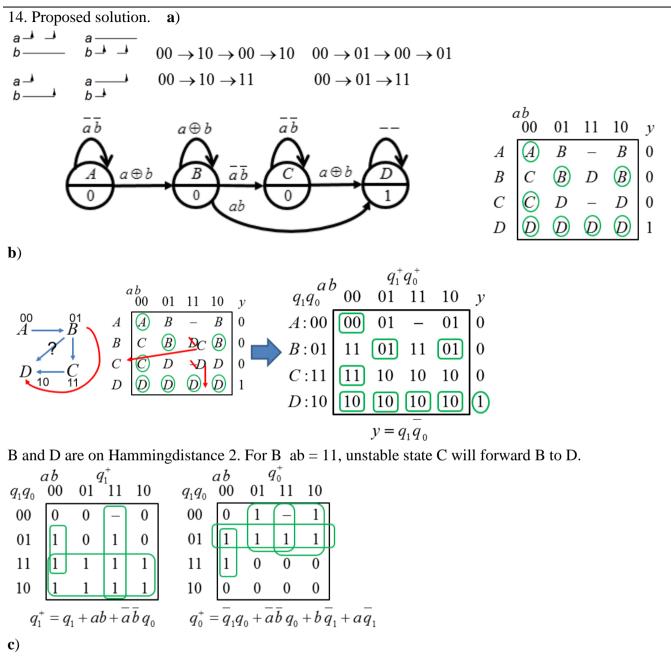

14. 5p Registration of double edges.

Pulses are received at two inputs *a* and *b* of an asynchronous sequential circuit. As soon as a total of two positive edges (transitions from  $0\rightarrow 1$ ) has been submitted to the inputs then the output *y* becomes 1 (and then remains 1 regardless of input signals).

Two edges means that it either enters two pulses to any of the inputs, or enters one pulse to each input. The pulses may come at any time to the inputs and no assumption can be made about the length of the pulses.

At start both input signals are a = b = 0. No simultaneous input signal changes can occur. a) (2p) Study the possible inputs, and set up a proper **flow table** for the sequential circuit. Draw the **state diagram**.

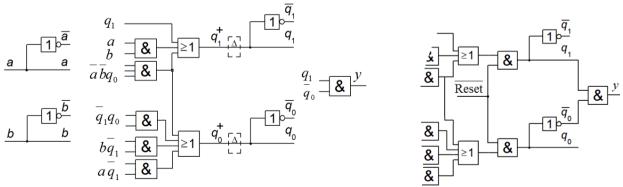

**b**) (2p) Make a suitable state assignment with an **exitation table** that provides circuits that are free from critical race (comment on how you achieved this). You will also develop the hazard free **expressions** for the **next state** (comment on how you achieved this) as well as an expression for **output**.

c) (0,5p) Draw the circuit diagram. (Use optional gates).

**d**) (0,5p) To be useful, the sequential circuit will need a Reset input so that it can be re-started. Complete the circuit with such a function. (Use optional gates).

d) An active low Reset could be inserted with two and-gates as the initial state A has the code 00.

# Good Luck!

# Submission sheet for Part A1 Sheet 1

( remove and hand in together with your answers for part A2 and part B )

| Last na  | ime:                                                                                                                                            | Given name:                        |    |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----|

| Person   | al code:                                                                                                                                        | Sheet:                             | 1  |

| Write    | down your answers for                                                                                                                           | the questions from Part A1 (1 to 1 | 0) |

| Question | Answer                                                                                                                                          |                                    |    |

| 1        | $f(x, y, z) = \{PoS\}_{\min} = ?$                                                                                                               |                                    |    |

| 2        | $x = 1010_2 \rightarrow y = k \cdot x = y_5 y_4 y_5$                                                                                            | $y_3y_2y_1y_0 = ?$                 |    |

| 3        | $x_{16} = \text{FFFB} \rightarrow 4\text{-bit} \rightarrow \pm x_{10}$                                                                          | $_{0} = ?$                         |    |

| 4        | $Y = \{SoP\}_{\min}$                                                                                                                            |                                    |    |

| 5        | Y = f(a, b, c, d)                                                                                                                               |                                    |    |

| 6        | F = f(A, B, C, D)                                                                                                                               |                                    |    |

| 7        |                                                                                                                                                 | $\ominus$ $\ominus$                |    |

| 8        | $q_2 q_1 q_0 = 000 \rightarrow \rightarrow \rightarrow ??$                                                                                      | 2                                  |    |

| 9        | $a \qquad A \qquad a_{0}^{1}$ $b \qquad b_{0}^{1}$ $b \qquad A \qquad $ |                                    |    |

| 10       | 02 <= (                                                                                                                                         | )                                  | ;  |

### This table is completed by the examiner!!

| <b>Part A1</b> (10) | Part A2 (10) |    | <b>Part B</b> (10) |    | <b>Total</b> (30) |       |

|---------------------|--------------|----|--------------------|----|-------------------|-------|

| Points              | 11           | 12 | 13                 | 14 | Sum               | Grade |

|                     |              |    |                    |    |                   |       |

|                     |              |    |                    |    |                   |       |