#### VHDL Testbench for ModelSim

#### Template -program action

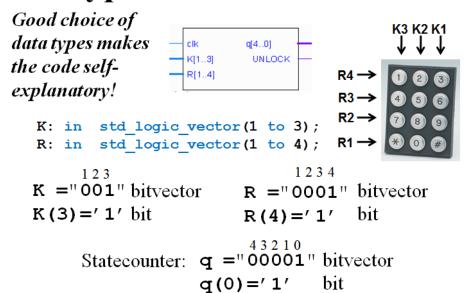

## **Keypad and Statecounter**

#### This code is given

```

library IEEE:

use IEEE.std_logic_1164.all;

output_decoder: -- output decoder part

use IEEE.std_logic_arith.all;

process (state)

begin

entity codelock is

case state is when 0 to 1 => UNLOCK <= '0';

in std_logic;

in std_logic_vector(1 to 3);

port( clk:

when 2 to 31 => UNLOCK <= '1';

in std_logic_vector(1 to 4);

out std_logic_vector(4 downto 0);

R:

end case;

q:

end process;

UNLOCK: out std_logic );

end codelock;

state_register: -- the state register part (the flipflops)

process(clk)

architecture behavior of codelock is subtype state_type is integer range 0 to 31;

begin

if rising_edge(clk) then

signal state, nextstate: state_type;

state <= nextstate;

end if:

nextstate decoder: -- next state decoding part

end behavior;

It's easy to see that this is correct!

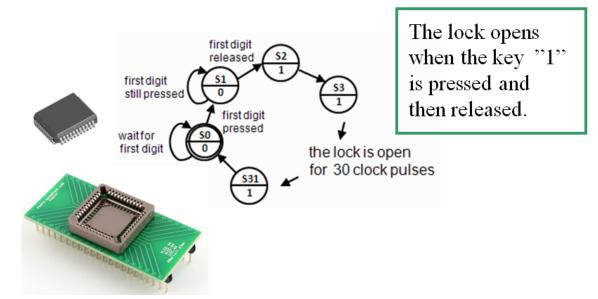

first digit

when 0 => if (K = "100" and R ="0001")

released

then nextstate <= 1;

else nextstate <= 0;

S1

end if;

when 1 => if (K = "100" and R = "0001")

0

still pressed

then nextstate <= 1;

elsif (K = "000" and R = "0000") then nextstate <= 2;

first digit

else nextstate <= 0;

pressed

end if;

waitfor

when 2 to 30 => nextstate <= state + 1;

first digit

the lock is open

=> nextstate <= 0:

when 31

for 30 clock pulses

531

end process:

debug_output: -- display the state

q <= conv_std_logic_vector(state,5);</pre>

```

# lockmall with error.vhd

```

library IEEE;

use IEEE.std_logic_1164.all;

debug_output: -- display the state

q <= conv_std_logic_vector(state,5);</pre>

use IEEE.std_logic_arith.all;

output_decoder: -- output decoder part

entity codelock is

process (state)

port( clk:

in std logic;

begin

in std_logic_vector(1 to 3);

in std_logic_vector(1 to 4);

out std_logic_vector(4 downto 0);

K:

when 0 to 1 => UNLOCK <= '0':

q: out std_logic_vec

UNLOCK: out std_logic );

when 2 to 31 => UNLOCK <= '1';

end case:

end process;

architecture behavior of codelock is

state register: -- the state register part (the flipflops)

subtype state_type is integer range 0 to 31;

signal state, nextstate; state type;

if rising_edge(clk) then

state <= nextstate;</pre>

nextstate decoder: -- next state decoding part

end if:

end process;

nextstate decoder: -- next state decoding part

end behavior;

process(state, K, R)

Now it's hard to see if this is correct or not?

begin

case state is

when 0 \Rightarrow if(((R(2)='0') \text{ and } (R(3)='0') \text{ and } (K(2)='0') \text{ and } (K(3)='1')) \text{ and } (\text{not } (((not ((K(1)='0') \text{ and } (R(1)='0') \text{ and } (R(4)='1'))) \text{ and } (R(4)='1')))

( not ((K(1)='1') \text{ and } (R(1)='1') \text{ and } (R(4)='0'))))))

then nextstate <= 1;

else nextstate <= 0;

end if;

when 1 \Rightarrow if(((R(2)='0') \text{ and } (R(3)='0') \text{ and } (K(2)='0') \text{ and } (K(3)='1')) and

( not (( not ((K(1)='0') and (R(1)='0') and (R(4)='1'))) and

( not ((K(1)='1') and (R(1)='1') and (R(4)='0'))))))

then nextstate <= 1:

elsif (K = "000" and R = "0000") then nextstate <= 2;

else nextstate <= 0;

end if;

when 2 to 30 => nextstate <= state + 1;

when 31

=> nextstate <= 0;

end process;

```

#### Does both expressions mean the same?

```

(K = "100" and R = "0001")

```

#### Is this really the same thing?

```

(((R(2)='0') \text{ and } (R(3)='0') \text{ and } (K(2)='0') \text{ and } (K(3)='1')) \text{ and } (not (( not ((K(1)='0') \text{ and } (R(1)='0') \text{ and } (R(4)='1'))) \text{ and } (not ((K(1)='1') \text{ and } (R(4)='0')))))))

```

Someone "promises" that the code is correct - but how can you know that this is absolutely true?

# tb\_lockmall.vhd

#### We need to write a VHDL-testbench

A test bench program can test all the possible key combinations and report if there is a problem ...

It can automatically loop through all possible key-presses and report on whether the lock trying to open or not.

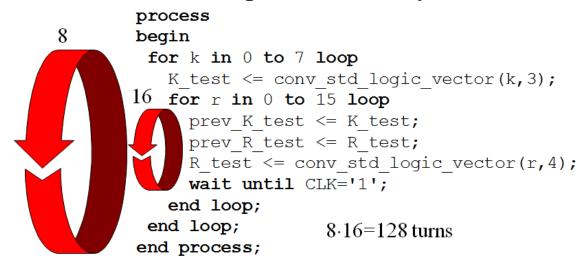

There are  $2^7 = 128$  possible key combinations and we'd be totally exhausted if we tried to test them all by hand.

# entity – a testbench has no ports

entity tb codelock is

- -- entity tb codelock has no ports

- -- because it's for simulation only

end tb codelock;

## Some internal signals are needed

## Our codelock is used as a component

## Generate a simulation clock

```

-- generate a simulation clock clk <= not clk after 10 ns;

T=20ns

f=50MHz

10ns

```

# Instantiatiation and signal mapping

## Two nested loops creates keystrokes

## report, severity note, severity error

Tests if state q = "00001" will be reached by any combination.

```

first digit

check:

process (q)

waitfor

begin if ((q = "00001") and

(prev K test = conv std logic vector(1,3)) and

(prev R test = conv std logic vector(1,4)))

then assert false report

"Lock tries to open for the right sequence!"

severity note;

else if ((q = "00001"))

then

assert false report

"Lock tries to open with the wrong sequence!"

severity error;

else report "Lock closed!" severity note;

end if;

end if;

end process check;

```

## Simulate and find the error!

What else besides pressing the "1" key could open the lock?

?